# 低消費電力3Dスタッキングメモリベースの ニューラルネットワークプロセッサ

会津大学 DANG Nam Khanh

### 目的

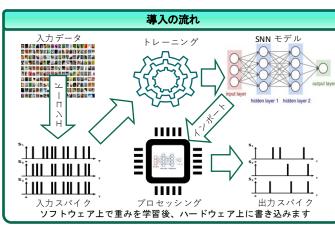

スパイキング・ニューラル・ネットワーク(SNNs)は、低消費電力かつ高性能である生物学的神経システムを模倣しています。本研究では、3次元ハードウェア・アーキテクチャと低消費電力設計技術を用いて、スパイキング・ニューラル・ネットワークの低消費電力の利点を活用することを目指します。

### 方法

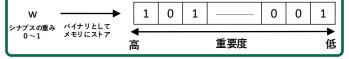

シナプスの重みの重要度を区別し、3次元構造の層を使ってそれらを分離するといった方法を用います。その結果、低消費電力技術に伴う問題は、重要性の低いビットにしか影響しません。したがって、性能を維持しつつ、消費電力を劇的に削減することができます。

# 概要アーキテクチャ (a) M\*\*Memory Die - M\*\* M\*\*Memory Die - M\*\* M\*\*Memory Die - M\*\* M\*\*Memory Die - M\*\* \*\*Synapse Val. \*\*June Memory Die - M\*\* \*\*Synapse Val. \*\*June Memory Die - M\*\* \*\*Synapse Val. \*\*June Memory Die - M\*\* \*\*Synapse Val. \*\*Logic Die - M\*\* \*\*Weight W, [0:n-1] = 11 1001 ... 1101 \*\*Layer M\*\* \*\*Logic Die - M\*\* \*\*Bits 11 1 001 - 01

## (a) 3次元構造 (b) ビット配置

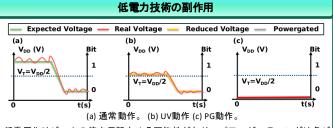

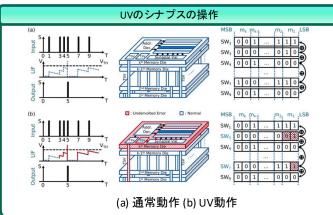

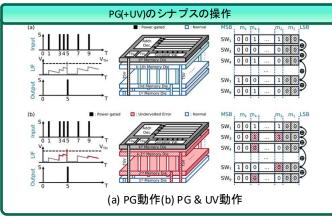

低電圧化はビットの値を反転させる可能性があり、パワーゲーティングは各ビ

ットの値をゼロにしてしまいます。

\*UV(Under Volted): 3D ICの層の電源電圧を下げる

\*PG(Power Gated): 3D ICの層の電源を切る

(a) 精度 (b) 消費エネルギー (c) ビットエラー率

精度 vs エネルギー ・ UV & PG:

(a) UV 2層 (b) PG 1層 & UV 2層 (c) PG 2層 & UV 2層