# 低消費電力 3Dスタッキングメモリベースの ニューラルネットワークプロセッサ

会津大学 DANG Nam Khanh

## 目的

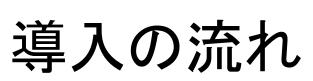

・スパイキング・ニューラル・ネットワーク(SNNs)は、低消費電力かつ 高性能である生物学的神経システムを模倣しています。本研究では、 3次元ハードウェア・アーキテクチャと低消費電力設計技術を用いて、 スパイキング・ニューラル・ネットワークの低消費電力の利点を活用 することを目指します。

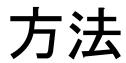

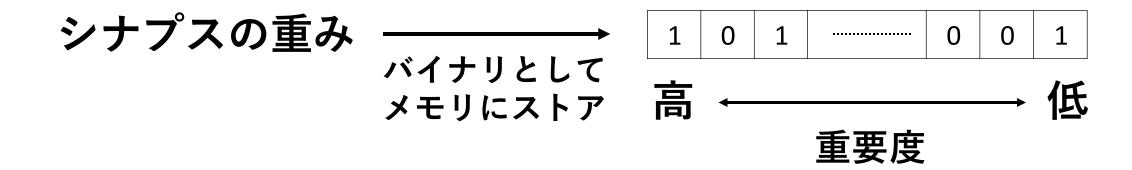

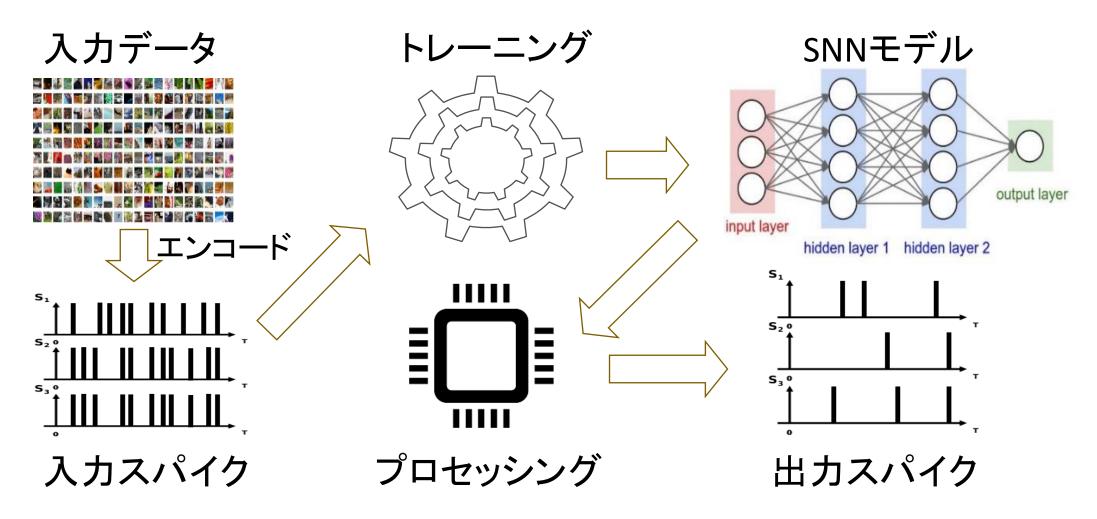

・シナプスの重みの重要度を区別し、3次元構造の層を使ってそれら を分離するといった方法を用います。その結果、低消費電力技術に 伴う問題は、重要性の低いビットにしか影響しません。したがって、 性能を維持しつつ、消費電力を劇的に削減することができます

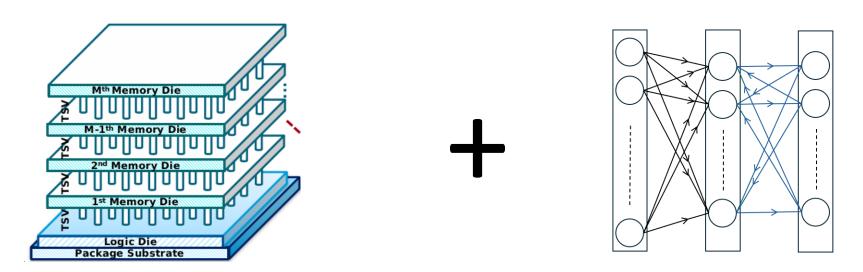

# 概要アーキテクチャ

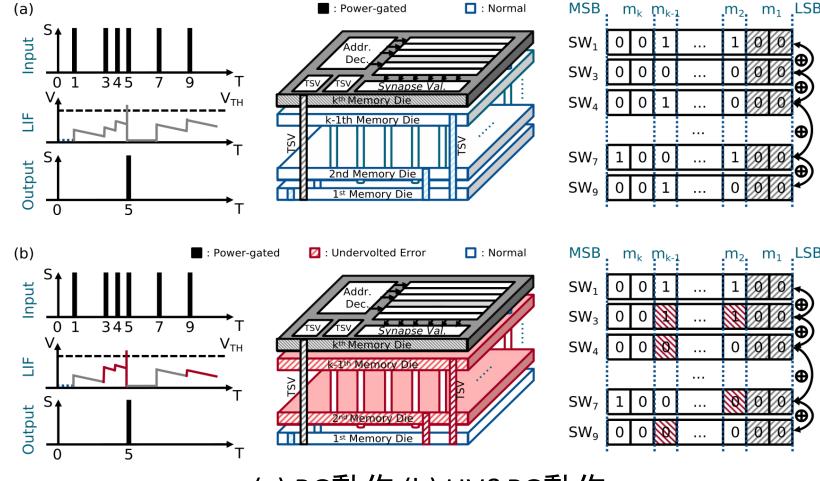

(a) 3次元構造 (b) ビット配置

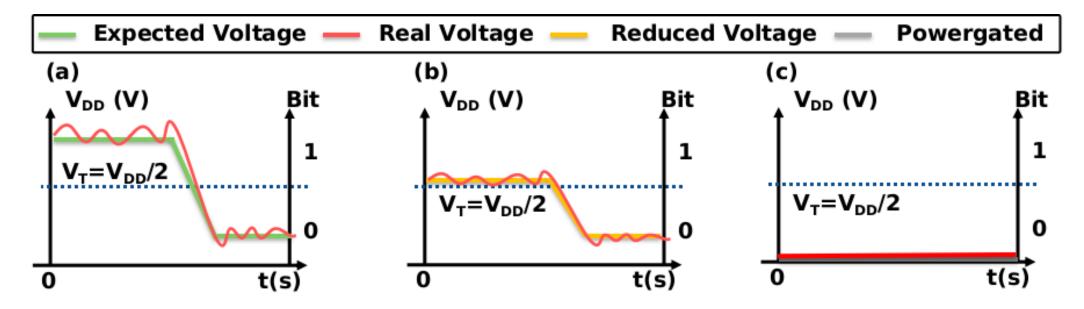

#### 低電力技術の副作用

低電圧化(b):ビット値が反転する可能性 パワーゲーティング(C):各ビットの値→ゼロ

(a) 通常動作 (b) UV動作 (c) PG動作

\*UV(Under Volted): 3D ICの層の電源電圧を下げる \*PG(Power Gated): 3D ICの層の電源を切る

ソフトウェア上で重みを学習後、ハードウェア上に書き込みます

## 低電圧(UV)時の動作

(a) 通常動作 (b) UV動作

(a) PG動作(b) UV&PG動作

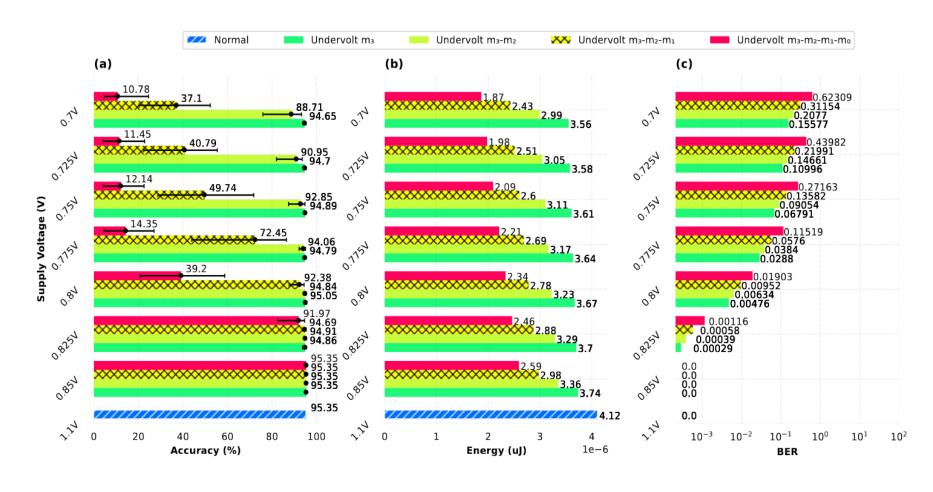

(a) 精度 (b) 消費エネルギー (c) ビットエラー率

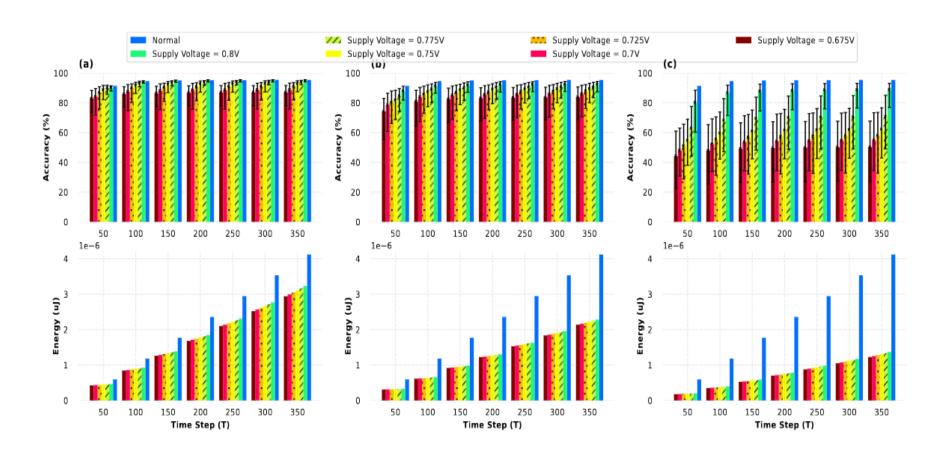

(a) UV 2層 (b) PG 1層 & UV 2層 (c) PG 2層 & UV 2層